1、反射问题概述

1.1 反射的产生

只要信号遇到瞬时阻抗突变,反射就会发生。反射可能发生在线的末端,或者是互联拓扑结构改变的地方,如拐角、过孔、T 型结构、连接件和封装处。为了保持信号的完整性,互联设计时要尽可能保持互联阻抗的恒定。

无论什么原因使瞬时阻抗发生了改变,部分信号将沿着与原传播方向相反的方向反射,另一部分将继续传播,但幅度有所改变。将瞬时阻抗发生改变的地方称为阻抗突变。反射信号的大小由瞬时阻抗的突变程度确定,如果第一区域的瞬时阻抗是Z1,第二区域是Z2,则反射信号与入射信号的强度之比为:

1.2 传输线突变

1.2 传输线突变

阻抗突变,必有反射。对突变进行准确预测,是为了选择更合适的设计方案。即使电路板在设计时考虑了可控阻抗互联,在下列情况下仍然不可避免地会遇到阻抗突变:线的两端;封装引线;接收器的输入门电容;信号层间的过孔;走线拐角;多分支线;短桩线;测试焊盘;返回路径上的间隙。传输线突变引起信号失真程度与两个重要因素有关:信号的上升沿和阻抗突变的大小。一般来说,反射噪声应控制在电压的10%之内。某些场合,反射噪声要求控制在5%以内。

过孔是串联突变的一个典型,过孔是传输中的瓶颈。走线宽度变窄,窄线条或颈状线使得特征阻抗变大。决定短线段对信号影响程度的三个要素是:信号的宽度、长度、和信号上升沿。即突变段的特征阻抗 Z0、突变段的时延 TD 和信号上升沿 RT。阻抗的突变引起了信号的振荡,从而形成了反射噪声。为此,必须设计均匀特征阻抗的互连。为了保持反射噪声小于电压的5%,必须要保持特征阻抗的变化率小于10%。如果突变段很短,两端产生的反射相互抵消,对整个信号完整性的影响可以忽略。

经验法则是信号突变段的长度(in)小于信号上升沿的长度(ns),此时可以忽略突变的影响。

并联突变即走线分支对信号的影响程度取决于两个因素:信号上升沿和分支的相对长度。短分支又称作桩线。信号遇到了分支点之后,相当于遇到了两端传输线的并联阻抗,此阻抗较低,将产生负反射。

经验法则是如果分支线长度小于信号上升沿空间延伸的20%,影响可以忽略,这是处理分支设计的首要原则。

1.3 上升时间对反射的影响

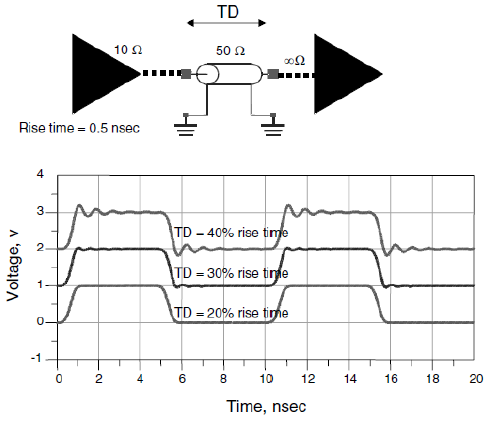

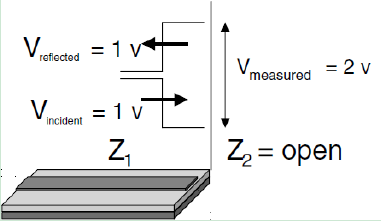

当上升时间小于两倍的传输时延(TD)时,上升时间将对波形产生严重的影响。下图分别显示了边沿变化率对过驱动传输线和欠驱动传输线的影响。过驱动是指驱动源内阻小于传输线阻抗,欠驱动是指驱动源内阻大于传输线阻抗。当上升时间大于两倍传输线时延时,其波形变化的剧烈程度减缓。

1.4 短线条不需要考虑匹配

1.4 短线条不需要考虑匹配

如果传输线很短,信号在接收器高阻开路和驱动器低内阻之间的反射被淹没在上升沿中了,此时接收端波形中看不出振铃。当传输线时延 TD 小于上升时间 RT 的20%时,接收端波形中几乎看不出振铃。 经验法则:当传输线时延 TD < 上升边的20%时,振铃可以忽略,传输线不需要匹配。当传输线时延 TD > 上升沿的20%时,就要考虑振铃噪声及匹配措施。那么在什么情况下要进行阻抗匹配呢?经验法则:当传输线长度的英寸(inch)值等于信号上升边的纳秒(ns)值时不需要考虑振铃,如果传输线更长就要考虑振铃。

经验法则:当传输线时延 TD < 上升边的20%时,振铃可以忽略,传输线不需要匹配。当传输线时延 TD > 上升沿的20%时,就要考虑振铃噪声及匹配措施。那么在什么情况下要进行阻抗匹配呢?经验法则:当传输线长度的英寸(inch)值等于信号上升边的纳秒(ns)值时不需要考虑振铃,如果传输线更长就要考虑振铃。

2、不同负载情况下的反射

2.1 电阻性负载的反射

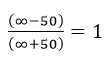

无损线的特征阻抗是纯电阻性,线上的电压与电流同相,其值与频率几乎无关。传输线的终端端接有三种最典型的情况:开路、短路、匹配。假设传输线的特征阻抗是 50Ω,信号由源端沿传输线达到有终端端接的远端。如果终端开路,末端的瞬时阻抗是无穷大,此时的反射系数为: 在开路端将产生与入射波大小相同,方向相反——返回源端的反射波。传输线开路末端的总电压,是两个波的叠加:一个是幅度为 1V 向开路端传播,另一个是向相反的源端方向传播的 1V 信号。

在开路端将产生与入射波大小相同,方向相反——返回源端的反射波。传输线开路末端的总电压,是两个波的叠加:一个是幅度为 1V 向开路端传播,另一个是向相反的源端方向传播的 1V 信号。

Figure 1 If the second impedance is an open, the reflection coefficient is 1. At the open, there will be two oppositely traveling waves superimposed.

如果传输线末端的信号线与返回路径短路,此时的末端阻抗为 0,反射系数为: 对于 1V 的入射信号,产生-1V的反射信号向源端传播,短路突变处的入射电压与反射电压之和为0。最后一种特殊情况是传输线末端所接电阻器与传输线的阻抗匹配,即传输线的末端端接50Ω电阻器,则反射系数为

对于 1V 的入射信号,产生-1V的反射信号向源端传播,短路突变处的入射电压与反射电压之和为0。最后一种特殊情况是传输线末端所接电阻器与传输线的阻抗匹配,即传输线的末端端接50Ω电阻器,则反射系数为 此时不存在反射,50Ω电阻器两端的电压就是入射信号。当末端为一般电阻性负载时,信号感受到的瞬时阻抗在 0 到 ∞ 之间,反射系数在 -1 到 +1 之间。下面介绍一个多次反射的例子,假设信号源是一个2V的信号,源端阻抗为25Ω,传输线阻抗为50Ω,传输线时延为250ps,则信号的反射计算及波形如下图所示。

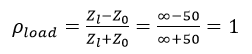

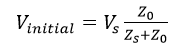

此时不存在反射,50Ω电阻器两端的电压就是入射信号。当末端为一般电阻性负载时,信号感受到的瞬时阻抗在 0 到 ∞ 之间,反射系数在 -1 到 +1 之间。下面介绍一个多次反射的例子,假设信号源是一个2V的信号,源端阻抗为25Ω,传输线阻抗为50Ω,传输线时延为250ps,则信号的反射计算及波形如下图所示。 由于负载端开路,负载端的反射系数为

由于负载端开路,负载端的反射系数为 源端的反射系数为

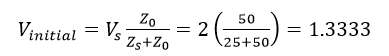

源端的反射系数为![]() ⑴ 在 0~250ps 阶段,信号源端的电压为

⑴ 在 0~250ps 阶段,信号源端的电压为 负载端的电压为0;

负载端的电压为0;

⑵ 在 250ps~500ps 阶段,信号源端的电压依然为1.33V,而负载端由于全反射电压翻番为2.66V,即1.33 + 1 × 1.33 = 2.66V;

⑶ 在 500ps~750ps 阶段,负载端反射回来的2.66V电压在源端进行了再次反射,源端电压为 2.66 + (-0.33)× (2.66 – 1.33)= 2.22V,负载端依然为2.66V

⑷ 在 750ps~1000ps 阶段,源端依然为2.22V,负载端首先达到源端电压2.22V,然后对其变化量乘以反射系数,即2.22 + 1 × (2.22 – 2.66)= 1.77V;

⑸ 在 1000ps~1250ps 阶段,源端首先会达到负载端的1.77V,然后叠加上反射量,即1.77 + (-0.33)×(1.77 – 2.22)= 1.92V,负载端保持 1.77V;

即负载端的电压为: 其中

其中![]() 为信号到达终端之后的电压值减去信号到达终端之前的电压值。源端的电压在第一次初始的时候是通过分压计算的,即

为信号到达终端之后的电压值减去信号到达终端之前的电压值。源端的电压在第一次初始的时候是通过分压计算的,即 当电压从负载端返回时,其电压计算公式为:

当电压从负载端返回时,其电压计算公式为:![]() 其中

其中![]() 为信号到达源端之后的电压值减去信号到达之前的电压值。下图是仿真的图形,仿真图形与计算结果一致。

为信号到达源端之后的电压值减去信号到达之前的电压值。下图是仿真的图形,仿真图形与计算结果一致。 欠驱动时的计算结果及仿真波形如下所示:

欠驱动时的计算结果及仿真波形如下所示:

2.2 容性负载与反射

实际的接收器有门输入电容,接收器封装引线与返回路径间约有 1pF 寄生电容。信号沿传输线到达末端理想电容时,反射系数中的瞬时阻抗 Z2 将随时间而变化,时域容抗为: 信号上升沿的初期变化率大,容抗小。即当电流刚到达电容时,电容可看作短路负载。随着电容器上 dv/dt 的下降,容抗增大,如果时间足够长,电容充满电后,电容器将相当于开路。假设信号传输延时为TD,从 t=TD 时刻开始,电容两端的电压由下式确定:

信号上升沿的初期变化率大,容抗小。即当电流刚到达电容时,电容可看作短路负载。随着电容器上 dv/dt 的下降,容抗增大,如果时间足够长,电容充满电后,电容器将相当于开路。假设信号传输延时为TD,从 t=TD 时刻开始,电容两端的电压由下式确定: 下图是一个负载容抗为10pF,传输线延时为500ps,驱动器和传输线特征阻抗都是50Ω,由下图可知,在 t 为 1ns(2TD)时,源端电压几乎将为 0。

下图是一个负载容抗为10pF,传输线延时为500ps,驱动器和传输线特征阻抗都是50Ω,由下图可知,在 t 为 1ns(2TD)时,源端电压几乎将为 0。 负载电容端的反射系数将从 0 变化到 1,反射信号将先下跌再上升到开路情形。上升沿为 0.5ns,当源端匹配而负载端的电容分别为0,2pF,5pF和10pF时,传输线上的波形如下图所示。当2.2ZoC与初始信号的上升沿相当时,远端的容性负载将对时序有明显的影响。

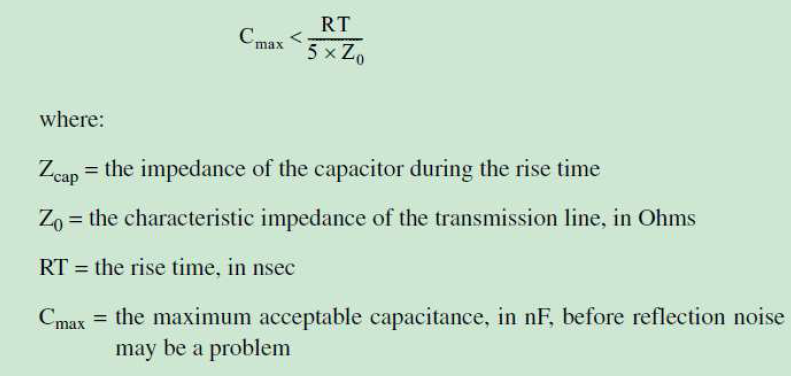

负载电容端的反射系数将从 0 变化到 1,反射信号将先下跌再上升到开路情形。上升沿为 0.5ns,当源端匹配而负载端的电容分别为0,2pF,5pF和10pF时,传输线上的波形如下图所示。当2.2ZoC与初始信号的上升沿相当时,远端的容性负载将对时序有明显的影响。 不仅负载电容会对信号产生影响,传输线上的集散电容也会对信号波形产生影响。测试焊盘,过孔,封装引线或连接到互连线中途的短桩线,都起着集总电容器的作用,这些电容将对传输线终端的信号产生影响。驱动器初始发出的信号没有受到什么影响,当信号到达终端发生反射后,将向源端返回,当再次到达电容器时,电压跌落部分将反射回终端,从而使得接收端信号下降形成下冲。

不仅负载电容会对信号产生影响,传输线上的集散电容也会对信号波形产生影响。测试焊盘,过孔,封装引线或连接到互连线中途的短桩线,都起着集总电容器的作用,这些电容将对传输线终端的信号产生影响。驱动器初始发出的信号没有受到什么影响,当信号到达终端发生反射后,将向源端返回,当再次到达电容器时,电压跌落部分将反射回终端,从而使得接收端信号下降形成下冲。 Figure 2 Reflected and transmitted signal in a transmission line circuit with a small capacitive discontinuity in the middle of the trace for a 0.5-nsec rise time and capacitances of 0.2pF, and 10pF.

Figure 2 Reflected and transmitted signal in a transmission line circuit with a small capacitive discontinuity in the middle of the trace for a 0.5-nsec rise time and capacitances of 0.2pF, and 10pF.

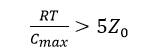

传输线中电容器的影响由信号上升时间和电容量决定,电容量越大,电容阻抗越小,负反射电压越大,从而接收端的下冲越大。上升时间越短,电容器阻抗越小,下冲将越大。如果要使得电容器阻抗对负载端信号的影响控制在某一范围内,必须对 RT/C 进行控制,其中 RT 为信号上升时间,C 为电容值,RT/C 描述了电容器的阻抗。传输线中的电容器相当于一个并联阻抗,当这个并联阻抗远大于传输线阻抗时,此电压下降变得很小。 由此得到:

由此得到: 假设 Z0 为 50Ω,则允许的最大电容为:

假设 Z0 为 50Ω,则允许的最大电容为: 为了避免容性负载突变造成过量的下冲噪声,应使电容量(pF)低于信号上升时间(ns)的 4 倍。容性负载产生的另外一个影响是使得终端信号接收时间被延迟,所以传输信号的10-90上升时间将增加,信号越过电压门限50%的时间也将增加,传输信号的10-90上升时间约为:

为了避免容性负载突变造成过量的下冲噪声,应使电容量(pF)低于信号上升时间(ns)的 4 倍。容性负载产生的另外一个影响是使得终端信号接收时间被延迟,所以传输信号的10-90上升时间将增加,信号越过电压门限50%的时间也将增加,传输信号的10-90上升时间约为:![]() 50%处的时延累加量约为:

50%处的时延累加量约为: 2.3 感性负载与反射

2.3 感性负载与反射

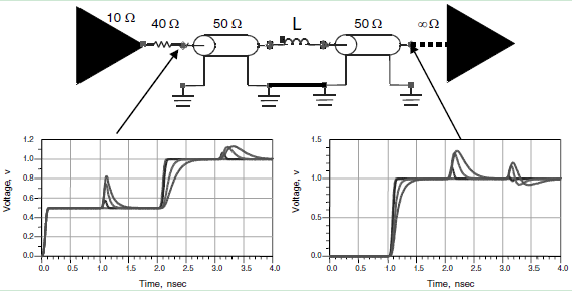

当传输线上出现串联电感时,该电感同样是与时间有关的负载。在初始 0 时刻,电感相当于开路负载。当电路中刚加入一个阶跃信号时,电感中几乎没有电流通过,这将产生反射,反射系数为 1。电感的大小将决定反射系数 1 能保持多久,如果电感量足够大,信号幅度将会翻倍。此后,电感释放能量,其放电速率取决于时间常数 L/Z0,下面是电感影响信号的波形图。 Figure 3 Signal at the source and the receiver with a 50-psec rise time interacting with an inductive discontinuity. Inductance values are L = 0, 1nH, 5nH, and 10nH.

Figure 3 Signal at the source and the receiver with a 50-psec rise time interacting with an inductive discontinuity. Inductance values are L = 0, 1nH, 5nH, and 10nH.

当信号的上升沿通过电感时,如果电感的阻抗小于特征阻抗,而且信号的上升沿是线性上升的,则电感的阻抗约为: 为了确保电感的阻抗小于导线阻抗的20%,可允许的最大阻抗突变约为:

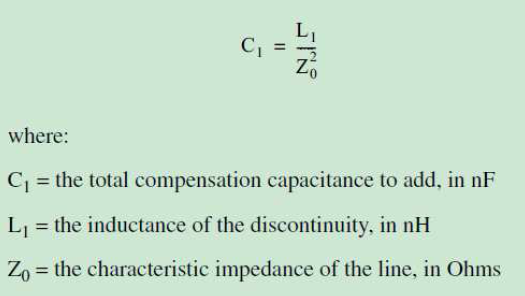

为了确保电感的阻抗小于导线阻抗的20%,可允许的最大阻抗突变约为: 为了补偿电感对信号产生的影响,可以在电感的两端并联小电容,为了最小化反射噪声,合适的电容值为:

为了补偿电感对信号产生的影响,可以在电感的两端并联小电容,为了最小化反射噪声,合适的电容值为: 3、消除反射的方案

3、消除反射的方案

3.1 减小反射的影响

传输线上的反射会对数字系统的性能产生严重的负面影响,为了将反射的负面影响降到最小,必须要采取措施抑制它们。本质上有三种方案可以降低反射的负面影响。第一种方法是降低系统频率,但此种方法会降低工作频率,减缓系统速度,故在高速系统中通常是难以接受的。第二种方法是缩短 PCB 走线,减少反射达到稳态所需要的时间,这种方法会增加成本,通常也不常用。第三种方法是在传输线的两端接一个与传输线特征阻抗相同的阻抗,以消除反射。

振铃是由源端和远端的阻抗突变,造成多次反射引起的。故只要在一端消除反射,就可以减少振铃噪声。在传输线的一端或两端进行阻抗端接,典型做法是在一端或两端放置一个电阻器或阻抗网络。如果一个驱动器驱动一个接收器,即点对点拓扑结构。将电阻器串联在驱动器端,称为源端串联匹配。此时,串接电阻加上驱动源内阻等于传输线特征阻抗。点到点拓扑的四种常用端接方式如下图所示,其中第一钟源端匹配最常用。

Figure 4 Voltage signal of a fast edge, at the far end of the transmission line with and without the source series terminating resistor.

Figure 4 Voltage signal of a fast edge, at the far end of the transmission line with and without the source series terminating resistor.

3.2 源端串联阻抗匹配

采用源端阻抗匹配是一种较好的匹配方式。如果源端不匹配,假设传输线阻抗为50Ω,驱动源内阻为10Ω,电压为1V。由于传输线上电压分压的关系,终端实际电压反而不到1V,为5/6V。终端的阻抗通常较高,这种高阻不易匹配。

如果源端单端匹配,而终端近似开路时,传输线分压所得的 1/2V在终端翻番成1V。当反射波返回源端时即被吸收,不再形成振铃,终端波形直接为1V的阶跃波形。

3.3 终端电阻匹配

使用一个电阻并联在传输线的终端,这种方法可以消除负载端反射。其缺点是大量的直流电流将会流向地,不利于功率传输和散热。而且其稳态电压是电源内阻与负载电阻之间的电压分配比决定的,需要更稳健的输出缓冲器。

3.4 终端交流匹配

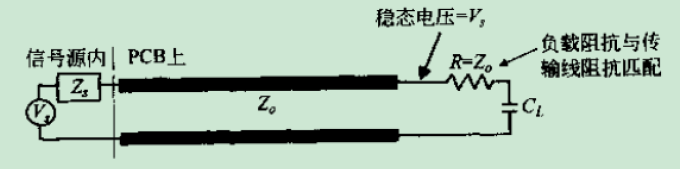

终端交流匹配是在传输线的终端,使用一个串联电容与串联电阻以消除反射,电阻R等于传输线的特征阻抗,电容CL应合理选择,使得负载端的RC时间常数等于一倍或两倍的上升时间。在刚开始电容相当于短路,传输线阻抗与电阻R匹配。电容充电,信号源达到稳态电压。优点是消除了负载端反射,且没有直流功耗,缺点是容性负载会增大信号的延迟,使负载端信号的上升下降时间延长。

3.5 常用的匹配方式

⑴ 消除高速信号反射可以采用串行端接的方式,在靠近源端的位置放置一个小电阻,使得驱动源端的内阻加上所串联的电阻值之和等于传输线的特征阻抗(此种端接方式的优点是功耗小,当驱动容性负载时可以提供限流作用,以减少地弹噪声,缺点是负载端的RC时间常数变大,上升沿变缓,不适合于高频信号通路,如高速时钟等);

⑵ 消除高速信号反射可以采用简单的并行端接,即在靠近负载端的位置加上拉或下拉阻抗以实现终端的阻抗匹配,最简单的并行端接方式是在负载端加一个下拉到地的电阻(前提是输出高电平时驱动端的输出能力要能够保证负载端电平高于高电平阈值);

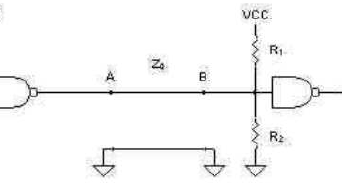

⑶ 并行端接的另外一种方式是戴维宁并行端接,采用上拉电阻 R1 和下拉电阻 R2 构成端接电阻,通过 R1 和 R2 吸收反射(R1 的最大值由可接受的信号的最大上升时间决定,与负载电容形成RC充电电路,R1的最小值由驱动源的灌电流数值决定,R2的选择应满足当传输线断开时电路逻辑高电平的要求,R1与R2并联后的阻抗值等于传输线阻抗时能够达到最佳匹配。此种方案尽管降低了对源端驱动能力的要求,但直流功耗较大);

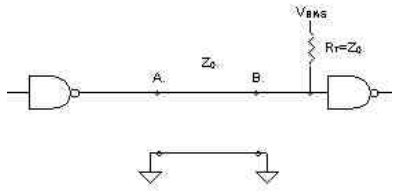

⑷ 主动并行端接策略中,端接电阻把负载信号拉至一偏移电压 Vbias,此种端接方式需要一个具有吸电流和灌电流能力的独立的电压源来满足输出电压的跳变速度的要求(此种接法也会有直流功耗);

⑸ 并行 AC 端接使用电阻和电容网络作为端接阻抗,端接电阻 R 要小于等于传输线阻抗 Z0,电容 C 必须要大于 100pF,推荐使用0.1uF的多层陶瓷电容(此端接方式无任何直流功耗);

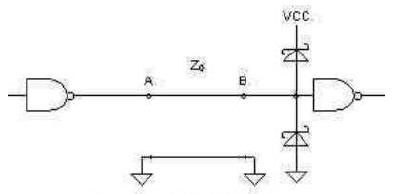

⑹ 并行端接时也可以采用肖特基二极管或快速开关硅管进行传输线端接,条件的二极管的开关速度必须至少比信号上升时间快4倍以上(此种接法的优点是使用二极管进行钳位,不再需要考虑精确控制传输线的阻抗匹配,缺点是二极管的开关速度一般很难做到很快,不适用于高速系统);

⑺ 多负载端接时,如果多个负载之间的距离较近,可通过一条传输线与驱动端连接,负载都位于传输线的终端,此时只需要一个端接电路。可以使用一个串联电阻进行串行端接,也可以在最远端进行并联端接(优先采用菊花链);如果多个负载相距较远,串联端接或并联端接要单独进行。