差分对是指一对存在耦合的传输线,采用两条信号线,让差分信号以差分对为载体进行传输。关于差分阻抗的详细定义请参考文末文献。

1、差分信号

1.1 差分信号的优点和缺点

差分信号传输与单端传输相比有很多优点:

- 输出驱动器产生的 dI/dt 会比单端信号线上大幅降低(电压低,阻抗又大一倍,接收器负载阻抗也大),从而减少了轨道塌陷和电磁干扰(EMI)的来源;

- 与单端放大器相比,接收器中的差分放大器可以有更高的增益;

- 差分信号在一对紧耦合差分对中传播,对付串扰和返回路径中突变的鲁棒性较好;

- 由于每个信号都有自己的返回路径,故差分信号通过接插件或封装时,不易受到开关噪声的干扰;

- 使用价格低廉的双绞线即可实现远距离传输;

- 与电源分配系统(PDS : Power Distribution System)的电源、地实现有效隔离。

其缺点包括:

- 存在导致 EMI 的潜在内因,一旦共模分量出现,可能使输出到外部双绞线上产生 EMI 问题;

- 与单端信号传输相比,传输需要两倍数量的信号线;

- 需要理解新原理和设计规则,设计复杂程度增加。

1.2 差分信号和共模信号

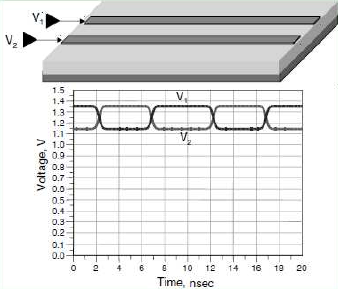

信号线和返回路径之间存在电压差,此电压信号称为单端传输信号。当两路驱动器驱动一个差分对时,除了各自的单端信号外,这两路信号线之间还存在着一个电压差,称之为差分信号。在低压差分信号(LVDS)中,每路电压范围在 1.125V 到 1.375V 之间,各自驱动一条传输线。 Figure 1 Voltage signaling scheme for LVDS signals, a typical differential signal.

Figure 1 Voltage signaling scheme for LVDS signals, a typical differential signal.

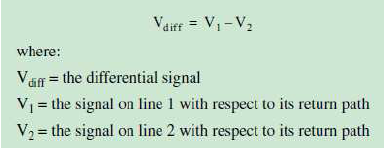

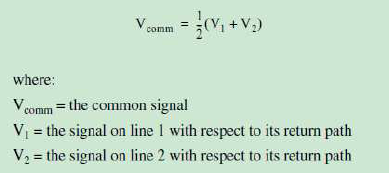

差分信号的电压为: 共模信号的电压为:

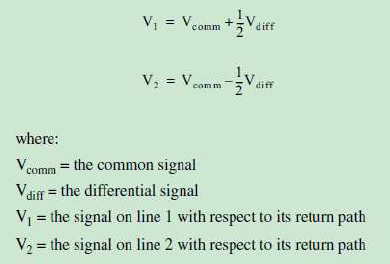

共模信号的电压为: 每条信号线与返回路径之间的单端电压可表示为:

每条信号线与返回路径之间的单端电压可表示为: 对于 LVDS 信号来说,差分信号在 -0.25 到 +0.25 之间,差分信号电压是 0.5V。共模电压分量也同样存在,它的均值为 1.25V,大于差分信号电压的两倍。通常情况下认为共模分量是恒定不变的直流,一个变化的共模分量将会潜在地引起两个严重的问题:⑴ 如果共模信号电压过高,就会使差分接收器的输入放大器饱和,使之不能准确读入差分信号;⑵ 变化的共模信号会引起 EMI,恒定的共模直流无害,不会出现问题。

对于 LVDS 信号来说,差分信号在 -0.25 到 +0.25 之间,差分信号电压是 0.5V。共模电压分量也同样存在,它的均值为 1.25V,大于差分信号电压的两倍。通常情况下认为共模分量是恒定不变的直流,一个变化的共模分量将会潜在地引起两个严重的问题:⑴ 如果共模信号电压过高,就会使差分接收器的输入放大器饱和,使之不能准确读入差分信号;⑵ 变化的共模信号会引起 EMI,恒定的共模直流无害,不会出现问题。

2、差分对及差分阻抗

2.1 差分对

两条单端传输线构成一个差分对,理论上说,任何两条传输线都可以构成一个差分对。差分对的特性如下:⑴ 差分对的横截面积是恒定不变的,对差分信号有一个恒定的阻抗,从而保证反射和失真达到最小;⑵ 每条线上的时延是相同的,从而确保了差分信号的边沿陡峭,如果两条传输线出现任何时延或错位,都会使部分差分信号变成共模信号;传输线的长度必须要完全相同,传输线的总长度相同能保证传输时延相同,使错位最小;⑶ 两条传输线的结构要完全相同,线的宽度和线间距要完全相同,即对称性。不对称会使差分信号变成共模信号;⑷ 差分对的两条线间耦合程度越强,差分信号就越不容易受到突变和非理想情况的影响。

2.2 无耦合时的差分阻抗

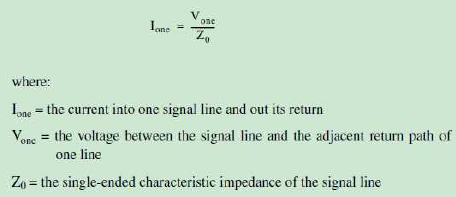

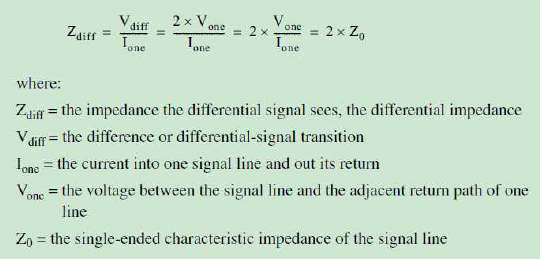

无偶合时的差分阻抗,即差分阻抗,是电压与电流的比值。假设差分对两条线之间不存在耦合,每条线的单端特征阻抗 Z0 为 50Ω。根据下式可以计算单端信号的电流: 对于 1V 的信号来说,第一条线的电流为 20mA,方向为从信号线流向返回路径。第二条线的电流也是 20mA,方向是从返回路径流向信号线。差分信号是一个 2V 跳变电压,如果仅着眼于这两条信号线,它们之间好像构成一个电流回路,20mA 的电流从一条信号线流出,再流入另一条信号线。根据阻抗的定义,差分信号的阻抗为:

对于 1V 的信号来说,第一条线的电流为 20mA,方向为从信号线流向返回路径。第二条线的电流也是 20mA,方向是从返回路径流向信号线。差分信号是一个 2V 跳变电压,如果仅着眼于这两条信号线,它们之间好像构成一个电流回路,20mA 的电流从一条信号线流出,再流入另一条信号线。根据阻抗的定义,差分信号的阻抗为: 即差分信号的阻抗是单端信号阻抗的 2 倍,如果单端信号阻抗是 50Ω,差分阻抗即为 100Ω。从信号线始端看进去,对每个驱动来说,信号线的阻抗都是 Z0,两信号线间的等效阻抗,称之为差分阻抗,是串联阻抗:

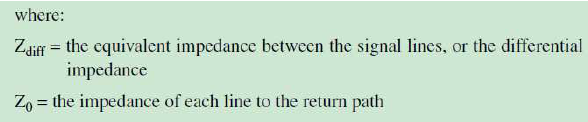

即差分信号的阻抗是单端信号阻抗的 2 倍,如果单端信号阻抗是 50Ω,差分阻抗即为 100Ω。从信号线始端看进去,对每个驱动来说,信号线的阻抗都是 Z0,两信号线间的等效阻抗,称之为差分阻抗,是串联阻抗:![]()

差分阻抗是单端阻抗的两倍,差分信号经差分对到达接收终端,在终端处所感受到的差分阻抗会非常大,使得差分信号反射回源端,差分信号在低阻抗的驱动端与高阻抗的信号线末端间会出现多次反射。消除反射的方法是在信号线的末端跨接匹配电阻,阻值为 2 × Z0。但是有两个因素会使得问题变得复杂:⑴ 两条线之间耦合的影响;⑵ 共模信号的作用以及它的产生与控制。

差分阻抗是单端阻抗的两倍,差分信号经差分对到达接收终端,在终端处所感受到的差分阻抗会非常大,使得差分信号反射回源端,差分信号在低阻抗的驱动端与高阻抗的信号线末端间会出现多次反射。消除反射的方法是在信号线的末端跨接匹配电阻,阻值为 2 × Z0。但是有两个因素会使得问题变得复杂:⑴ 两条线之间耦合的影响;⑵ 共模信号的作用以及它的产生与控制。

2.3 差分线耦合的影响 如上图带状线截面以及等效电容电路模型中,当两条信号线靠近时,信号线 1 和返回路径之间的边缘场被邻近的信号线阻断,故 C11 减小,C12 增加。但负载电容 CL=C11+C12 却没有较大的变化。当两条信号线靠近时,由于邻近导线的感应涡流,自感 L11 将略微减小,互感 L12 将增加。由于两线间距小,耦合 C12/CL 或 L12/L11 就强,但最大耦合度也不到 15%。当两线很远时,线 1 的特性阻抗与另一条无关,特性阻抗与 C11 成反比。

如上图带状线截面以及等效电容电路模型中,当两条信号线靠近时,信号线 1 和返回路径之间的边缘场被邻近的信号线阻断,故 C11 减小,C12 增加。但负载电容 CL=C11+C12 却没有较大的变化。当两条信号线靠近时,由于邻近导线的感应涡流,自感 L11 将略微减小,互感 L12 将增加。由于两线间距小,耦合 C12/CL 或 L12/L11 就强,但最大耦合度也不到 15%。当两线很远时,线 1 的特性阻抗与另一条无关,特性阻抗与 C11 成反比。

2.4 差分对返回电流的分布

对于一对差分线来说,如果返回导体距信号线足够远,那么差分信号的返回导体电流分布会相互重叠,相互抵消。此时返回路径的存在与否,对差分阻抗没有影响,但有三种情况需要注意:⑴ 边缘耦合微带线,返回平面足够远;⑵ 双绞线电缆;⑶ 宽边耦合带状线,返回平面足够远。

对于差分微带线来说,信号线间距最小时,返回平面中将有明显的电流分布,平面的存在将影响差分阻抗。如果将平面移到更远处,每条线的单端特性阻抗可能更将会增加,差分阻抗也将会增加。根据经验法则,当信号线与返回路径之间的距离大于等于两信号线边缘距离时,返回路径平面内电流会相互重叠,返回路径平面的存在对信号线的差分阻抗逐渐没有影响。此时,对差分信号而言,一条信号线的返回电流可看作由另一条信号线传送。

对于屏蔽双绞线来说,每条信号线的返回路径都是屏蔽层。当两条双绞线都近似位于屏蔽层的中心而且由差分信号来驱动时,它们的返回电流朝相反方向流动而且相互重叠,屏蔽层中将没有剩余电流分布。此时屏蔽层产生不了电效应,可以将其除去。对于差分阻抗来说,屏蔽层起不到任何作用,屏蔽层的一个重要作用是为共模电流提供了一个返回路径,从而降低了它的辐射效应。

对于差分带状线来说,当信号线与最近平面的间距大于 2 倍信号线间距时,差分阻抗与平面的位置无关。

以上实例说明信号线与返回平面间的耦合度大于两信号线间的耦合度时,返回路径平面中出现明显的返回电流。平面在确定差分阻抗时起到了重要作用。当两信号线间的耦合度远大于信号线与返回电流平面的耦合度时,平面中的大部分返回电流会重叠、抵消。这种情况下,平面影响不到差分阻抗。此时第一条线的返回电流将可以看作由第二条信号线来传送。根据经验法则,要使差分带状线两信号线间的耦合度大于信号线与返回平面间的耦合度,则信号线与最近平面间的距离必须要大于两信号线跨距的 2 倍。

3、信号完整性 Checklist

3.1 高速信号的反射

- 信号无论在何处遇到阻抗突变都会发生反射并使信号失真,只要传输线的长度(in)比信号上升时间(ns)长,就需要进行阻抗匹配,以消除振铃噪声;

- 当判断需要进行阻抗匹配时,源端匹配时最常用的一种匹配方式,即在源端串联电阻,并使电阻值与源阻抗值之和等于导线的特征阻抗;

- 为了保证信号反射噪声小于 5%,应保证导线特征阻抗的变化小于 10%。

- 对于一段长的传输线,如果有一小段突变,当突变的长度(in)小于信号上升时间(ns),突变造成的反射就不会引发问题;在一条传输线上会有短的桩线,如测试点引线,当短桩线的长度(in)小于信号上升时间(ns),短桩线造成的反射就不会引发问题;

- 传输线的中途会有寄生电容,如果容性突变电容量(pF)大于信号上升时间(ns)的 4 倍,就会造成过量的反射噪声。容性负载引起的时延累加约为电容量的 25 倍;

- 传输线的中途会有等效电感,可允许的感性突变值(nH)约为信号上升时间(ns)的 10 倍。在电感的两侧添加电容,可以平衡电感对传输线造成的影响;

3.2 高速信号的串扰

- 在布线限制允许的情况下,尽量加宽走线间距,以减少线间的寄生电容,从而降低容性串扰;

- 传输线设计中,在保证目标阻抗的同时,使导线尽可能的接近地,从而使得传输线与地平面紧密耦合,减小与相邻走点的耦合程度,也可以在串扰严重的两条线之间加入一根地线;

- 如果系统设计允许,对要求苛刻的网络(如时钟系统),使用差分布线技术,即信号线伴随着地线进行走线;

- 如果不同层的信号之间存在严重耦合,使这两层上的布线相互正交;

- 把信号线并行走线的长度将为最短,以短平行段布线,并使网络间的长耦合段降到最少;

- 合理分布电路板上的元件,将走线拥挤程度降到最低;

- 感性串扰发生在两个环路之间,尽量减少环路面积,如果允许的话,消除这个环路。不同的信号之间不要共用回路;

- 如果有可能,信号线尽量设计成带状线或埋式微带线,以获得较好的串扰抑制效果;

- 在满足设计要求的情况下,尽量选用边沿速率较慢的器件,其对串扰的影响最大;

3.3 DDR 相关设计原则

- 当使用 DDR 或 DDRII 时,建议采用 “T” 形走线,DDRIII 一般采用 “Fly-By” 方式走线;

- DDR 中 VREFDQ 与 VREFCA 信号与其他信号的距离至少为 15mil-25mil,VREF的走线要尽量粗,尽量短。Micron 推荐 20mil-25mil,在靠近设备端的 VREF 引脚处放置 100nF 的电容;

- DDR 中的时钟差分对要等长(<50mil),与其他走线之间需要 25mil 的安全距离。如果系统中有两个时钟,两个时钟之间相差 100mil 之内;

- DDR 中的地址线不用等长,比时钟线要长一些,控制线比时钟线要长一些;

- DDR 中每一个 Data Group (DQ+DQS+DM)在同一层走线,DQ 与 DQS 是源同步关系,做等长处理,同组的数据线以 DQS 为基准等长(<50mil)。组与组之间的长度差不超过 1000mil。DQS 与 CK 之间的约束关系较弱,一般不予考虑,长度差不超过 1000mil 即可;

- DDR 中 DQS 的布线位置在数据信号组内同一信号组中 DQ 走线的中间,DQS 与 DQS 之间的间距一般不关系;

- DDR 中 DQS 与时钟信号线不相邻;

- DDR 中为了避免串扰,数据信号组与地址/命令/控制信号组之间的走线间距至少是 20mil,建议它们在不同的信号层走线;

- DDR 中为了抑制 EMI, 时钟信号线尽量走在内层,CK 与 CK# 必须在同一层布线,误差不超过 20mil;

4、参考文献