电源完整性(Power Integrity)简称 PI,是确认电源来源及目的端的电压及电流是否符合需求。电源完整性在现如今的电子产品中相当重要。电源完整性囊括以下层面:芯片层面、芯片封装层面、电路板层面及系统层面。在电路板层面的电源完整性需达到以下三个需求:

- 使芯片引脚的电压纹波比规格要小一些(如电压和 1V 之间的误差小于±50mV);

- 控制接地反弹(亦称之为同步切换噪声 SSN、同步切换输出 SSO);

- 降低电磁干扰(EMI)并且维持电磁兼容性(EMC):电源分布网络(PDN)是电路板上最大型的导体,故亦为最易发射及接收噪声的天线。

1、同步开关噪声

1.1 同步开关噪声的产生

在高速数字电路中,内部的门电路会发生从高到低或从低到高的状态转换。在变化的过程中,门电路中的晶体管不停地导通和截止,这时会有电流从所接电源流入门电路,或从门电路流入地线,使电源线或地线上的电流产生不平衡,产生一个瞬间变化的电流 ΔI。这个电流在流经回流路径上存在的电感时会形成交流电压将,进而引起噪声。如果发生转换的输出缓冲器较多时,就会导致电源完整性问题,这种噪声称为同步开关噪声。

同步开关噪声主要是伴随着器件的同步开关输出而产生,开关速度越快,瞬间电流变化越显著,电流回路上的电感越大,则产生的同步开关噪声越严重。同步开关噪声电压表示公式如下:![]() 其中 N 表示同步开关的驱动器数目, Lloop 为整个回流路径上的电感,i 是每个驱动器的电流,Vssn是同步开关噪声的大小。

其中 N 表示同步开关的驱动器数目, Lloop 为整个回流路径上的电感,i 是每个驱动器的电流,Vssn是同步开关噪声的大小。

1.2 信号的返回路径

信号在信号线与参考面之间传播,不是只在信号线上传播。故参考面的物理特性与信号线的物理特性同等重要。传输到系统中的任何电流必须要返回信号源。电流通过最小的通路返回,在大多数情况下是电感最小的通路。当回路中存在不连续时,环路的面积会增大,由于电流必须要绕过不连续区域。电流环路面积的增大将导致电感的增加,从而降低信号完整性。回路不连续最主要的影响是串联电感会增大,该电感的幅值取决于电流返回时必须要迂回的长度。

在下图的例子中,CMOS输出驱动微带传输线时,考虑电流如何返回的问题。当系统从低电平跳变为高电平时,地平面上的返回电流必须要流经整个电容以完成回路。此处的电容表示本地去耦电容,通常位于芯片上或芯片附近,如果电容值不够大,或通路中有较大的电感,或通路中最近的去耦电容距离较远,将会对信号完整性产生不利的影响。 在进行系统设计时,必须要仔细研究返回路径,选择合适的叠层,使通过去耦电容的瞬时返回电流最小。一个典型的CMOS输出缓冲器从电源和地拉出的电流相等,信号布线的最佳方案是使用对称带状线,同时以电源和地为参考,此时流过去耦电容的最大电流将为 (1 / 2)I。

在进行系统设计时,必须要仔细研究返回路径,选择合适的叠层,使通过去耦电容的瞬时返回电流最小。一个典型的CMOS输出缓冲器从电源和地拉出的电流相等,信号布线的最佳方案是使用对称带状线,同时以电源和地为参考,此时流过去耦电容的最大电流将为 (1 / 2)I。

1.3 减小同步开关噪声的措施

由于芯片封装与电源平面的电感和电阻会引发电源噪声,电源噪声将会在地平面上引起电压波动,此波动会对电源或地引线上的其它器件构成严重的干扰,甚至引起错误的触发。负载电容的增加,负载电阻的减少,地电感的增大和开关器件数目的增加会导致同步开关噪声的增大。可以采用下面的措施减小同步开关噪声:

- 增大信号的翻转时间;

- 合理布局电源和地引脚,对于一个芯片有多个电源和地引脚时,同等对待电源和地引脚;

- 使用差分信号线传输信号可以抑制流过寄生参数器件的电流。

只有构成回路,电路才能工作,每条信号线上的电流必须要找一条路径从末端回到源端,一般选择与之相近的平面。在信号速率很低时,回流沿最小的通路,当速率较高时,回流沿电感最小的通路。返回通路位于接地层上,当电流到达驱动元件时,旁路电容会提供通向正确电压层的通路。为了维护良好的信号质量,需要提供一个干净的畅通无阻的返回通路。

2、电源分配网络

2.1 目标阻抗法概述

电源分配网络系统的作用是给系统内所有的器件或芯片提供足够的电源,并满足系统对电源稳定性的要求。为了保证每个器件始终都能得到正常的电源供应,需要对电源分配系统的阻抗进行合理的控制,尽可能降低其阻抗,使其在整个频率范围内的阻抗低于目标阻抗,即通常所说的电源分配系统目标阻抗法。

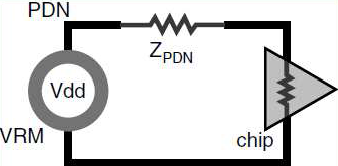

PCB的电源分配系统建模图如下所示,由电压调节模块、电源 / 地平面对和各种电容组成。这些组件在控制电源分配系统阻抗时,分别在不同的频率范围内最有效。电源模块响应的频率范围是 DC~1KHz,电解电容在 1KHz~1MHz 内保持较低阻抗,高频陶瓷电容在 1MHz~几百MHz内保持较低阻抗,而PCB的电源和地平面则在100MHz频率以上发挥重要作用。

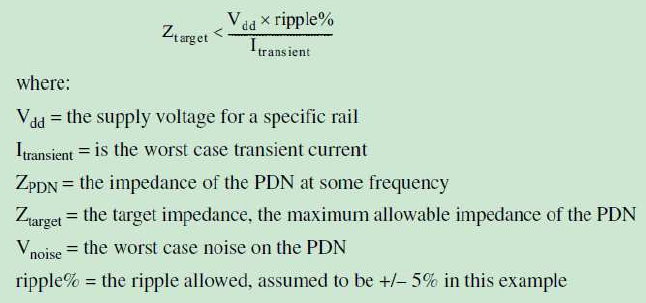

2.2 目标阻抗法计算

对于一个电源分配网络,有驱动源、串联阻抗和负载组成,如下图所示。当负载电流突变时,在串联阻抗上会产生一个压降,此压降要小于所允许的纹波电压。为了降低实际的纹波电压值,要么是降低串联阻抗值,要么是减小负载电流突变值。而负载电流突变值通常是不能降低的,只有控制串联阻抗,把串联阻抗值控制在目标阻抗值之下,即可把纹波电压值控制在某一特定值之下。 Figure 1 Diagram of the connections from the VRM(Voltage Regulator Module), through the PDN to the chip pads and the voltage drop across the PDN interconnects due to the impedance of the PDN.

Figure 1 Diagram of the connections from the VRM(Voltage Regulator Module), through the PDN to the chip pads and the voltage drop across the PDN interconnects due to the impedance of the PDN. 目标阻抗值如下:

目标阻抗值如下: 下面给出一个使用目标阻抗计算电容量的例子:

下面给出一个使用目标阻抗计算电容量的例子:

为了清楚的说明电容量的计算方法,举例如下。要去耦的电源为1.2V,容许电压波动为2.5%,最大瞬态电流 600mA。

第一步:计算目标阻抗

第二步:确定稳压电源频率响应范围

和具体使用的电源芯片有关,此处电源频率响应范围界限为100KHz。在100KHz以下时,电源芯片能很好的对瞬态电流做出反应,高于100KHz时,表现为很高的阻抗,如果没有外加电容,电源波动将超过允许的2.5%。为了在高于100KHz时仍满足电压波动小于2.5%要求,应该加多大的电容?

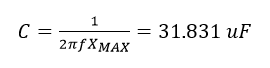

第三步:计算 Bulk 电容量

当频率处于电容自谐振点一下时,电容的阻抗可近似表示为:![]() 频率 f 越高,阻抗越小,频率越低,阻抗越大。在感兴趣的频率范围内,电容的最大阻抗不能超过目标阻抗,故使用 100KHz 计算(电容起作用的频率范围的最低频率,对应电容最高阻抗)。

频率 f 越高,阻抗越小,频率越低,阻抗越大。在感兴趣的频率范围内,电容的最大阻抗不能超过目标阻抗,故使用 100KHz 计算(电容起作用的频率范围的最低频率,对应电容最高阻抗)。 第四步:计算 Bulk 电容的最高有效频率

第四步:计算 Bulk 电容的最高有效频率

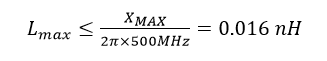

当频率处于电容自谐振点以上时,电容的阻抗可近似表示为:![]() 频率 f 越高,阻抗越大,但阻抗不能超过目标阻抗。假设 ESL 为 5nH,则最高有效频率为:

频率 f 越高,阻抗越大,但阻抗不能超过目标阻抗。假设 ESL 为 5nH,则最高有效频率为: 这样一个大的电容能够让我们把电源阻抗在 100KHz 到 1.6MHz 之间控制在目标阻抗之下。当频率高于 1.6MHz 时,还需要额外的电容来控制电源系统阻抗。

这样一个大的电容能够让我们把电源阻抗在 100KHz 到 1.6MHz 之间控制在目标阻抗之下。当频率高于 1.6MHz 时,还需要额外的电容来控制电源系统阻抗。

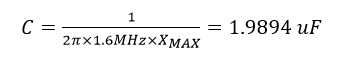

第五步:计算频率高于 1.6MHz 时所需电容

如果希望电源系统在 500MHz 以下时都能满足电压波动要求,就必须控制电容的寄生电感量。必须满足:![]() 故有:

故有: 假设使用 AVX 公司的 0402 封装陶瓷电容,寄生电感约为 0.4nH,加上安装到电路板上后过孔的寄生电感,假设为 0.6nH,则总的寄生电感为 1nH。为了满足总电感不大于 0.16nH 的要求,我们需要并联的电容个数为:1 / 0.016 = 62.5个,故需要 63 个0402电容。

假设使用 AVX 公司的 0402 封装陶瓷电容,寄生电感约为 0.4nH,加上安装到电路板上后过孔的寄生电感,假设为 0.6nH,则总的寄生电感为 1nH。为了满足总电感不大于 0.16nH 的要求,我们需要并联的电容个数为:1 / 0.016 = 62.5个,故需要 63 个0402电容。

为了在 1.6MHz 时阻抗小于目标阻抗,需要电容量为: 故每个电容的电容量为 1.9894 / 63 = 0.0316 uF。综上所述,对于这个系统,我们选择 1 个 31.831 uF 的大电容和 63 个 0.0316 uF 的小电容即可满足要求。

故每个电容的电容量为 1.9894 / 63 = 0.0316 uF。综上所述,对于这个系统,我们选择 1 个 31.831 uF 的大电容和 63 个 0.0316 uF 的小电容即可满足要求。

3、电源完整性 Checklist

3.1 电源分配网络中的电源和地噪声

- 使电源平面和地平面相邻并尽量靠近,以减少电源和地之间的回路电感;

- 使同相电流相邻间隔尽量远,而反向电流相隔尽量近;

- 电源过孔与地平面过孔尽量靠近,使它们的间隔至少与过孔的长度相当;

- 将电源平面和地平面尽可能靠近去耦电容所在的表面处,另外,使去耦电容焊盘间的布线和过孔尽可能短而宽;

- 在低频时使用一定量的去耦电容来代替稳压器件,在高频时使用一定量的去耦电容来抵消等效电感;

- 如果可能,对于至关重要的信号(如选通信号和时钟信号),使用差分输出驱动器和接收器。这样会消除共模噪声,并使得信号质量显著提高;

- 使片上电容足够大,使得电路中的瞬时能量不会被通路中电感所隔离,如果片上电容足够大,其行为就像一个本地电源,可以提高所需要的瞬时电流;

- 合理分配 I/O 引脚,使得局部群聚在一起的输出引脚数最少,在选用引脚布局时,应该使得信号引脚和电源/接地引脚之间的耦合最大。电源引脚和接地引脚放置在一起,以减少回路总电感;

- 减慢边沿变化率,但这将使得内核噪声耦合到预驱动电路中的概率增大,从而引起抖动;

- 为处理器的内核和 I/O 提供不同的供电电源,会使得同步开关噪声耦合到内核的概率降为最小,也将使得门电路状态开关发生错误的可能性降为最小;

- 尽可能减小通路中的电感,可以使用较宽的电源走线和较短的焊丝,来达到这个目的;

- 最小化去耦电容的电感;

- 为 PCB 走线选择合适的参考面,使得通过去耦电容的电流尽可能地小。

3.2 PCB 叠层与布局布线设计

- 为了保证良好的信号参考平面,尽量使用电源层和地层将信号层分开;

- 所有信号层尽可能与地平面相邻,确保关键信号层与地层相邻;

- 按照功能和类型布局,高速与低速分开,噪声敏感区单独隔离,数字与模拟分开;

- 在布线前分割数字地与模拟地;

- 按照线宽、线长、线间距约束要求来布线,尽量避免长的平行走线;

- 关键信号,高速信号如时钟信号尽量走内层,可以有效抑制垂直方向上的 EMI;

- 走线尽量少换层,对于同一组信号线,最好布在同一层;

- 走线越短越好,一般以时钟线为参考,长走线更容易引起信号完整性问题;

- 走线应尽量避免走锐角、直角,防止产生天线;

- 输入输出信号尽量避免相邻平行走线,最好在线间加地线,以防止反馈耦合,并远离高速和关键信号;

- 相同属性的一组总线,并排走线,并尽量等长;

- 差分线等距等长,并且远离其他信号线,特别是时钟等高速信号网络;

- 晶振的两条走线需拓扑结构相等,且尽量等长;

- 数字地与模拟地线要分开,对低频电路,接地应尽量采用单点并联接地,高频电路宜采用多点串联接地,对于数字电路,地线应闭合环路,以提高抗噪声能力;

- 打过孔需要考虑保持地层和电源层的完整性,不能太紧密造成平面断槽,那样容易造成信号回流的阻断,导致 EMI 问题;

- 对电源层的分割需要考虑,若信号以电源层为参考层的话,分割时不能阻断信号的回流路径;

- 电源层和地层的分割越少越好,尽量保持其完整性;

- 电源层的分割需要考虑为退耦电容留有足够宽的电流通路,以免窄的信号通路造成阻抗突变,形成压降,导致可能的供电不足,或者形成大的分布电感,使退耦电容的谐振点漂移;

- 在大电流的铜皮上多大过孔,以满足电流需求;

- 高频信号的线长应该是比较短的;